TFT Customization

LinkZill provides TFT customized services and compatible

electronic system design for customers to meet

their R&D and production needs.

TFT Customization

LinkZill provides TFT customized services and compatible electronic system design for customers to meet their R&D and production needs.

TFT Device Customization

LinkZill’s dedicated TFT design team brings deep technical expertise and hands-on experience to every project. From technical consultation to responsive post-sale support, LinkZill always provides professional, high efficient service for customers at every stage — ensuring quality, reliability, and long-term satisfaction.

LinkZill helps the customers to choose the most suitable TFT technology to meet their requirements and design the TFT chips for sensor array detection, active matrix display, and compute-in-memory, providing end-to-end technical solutions.

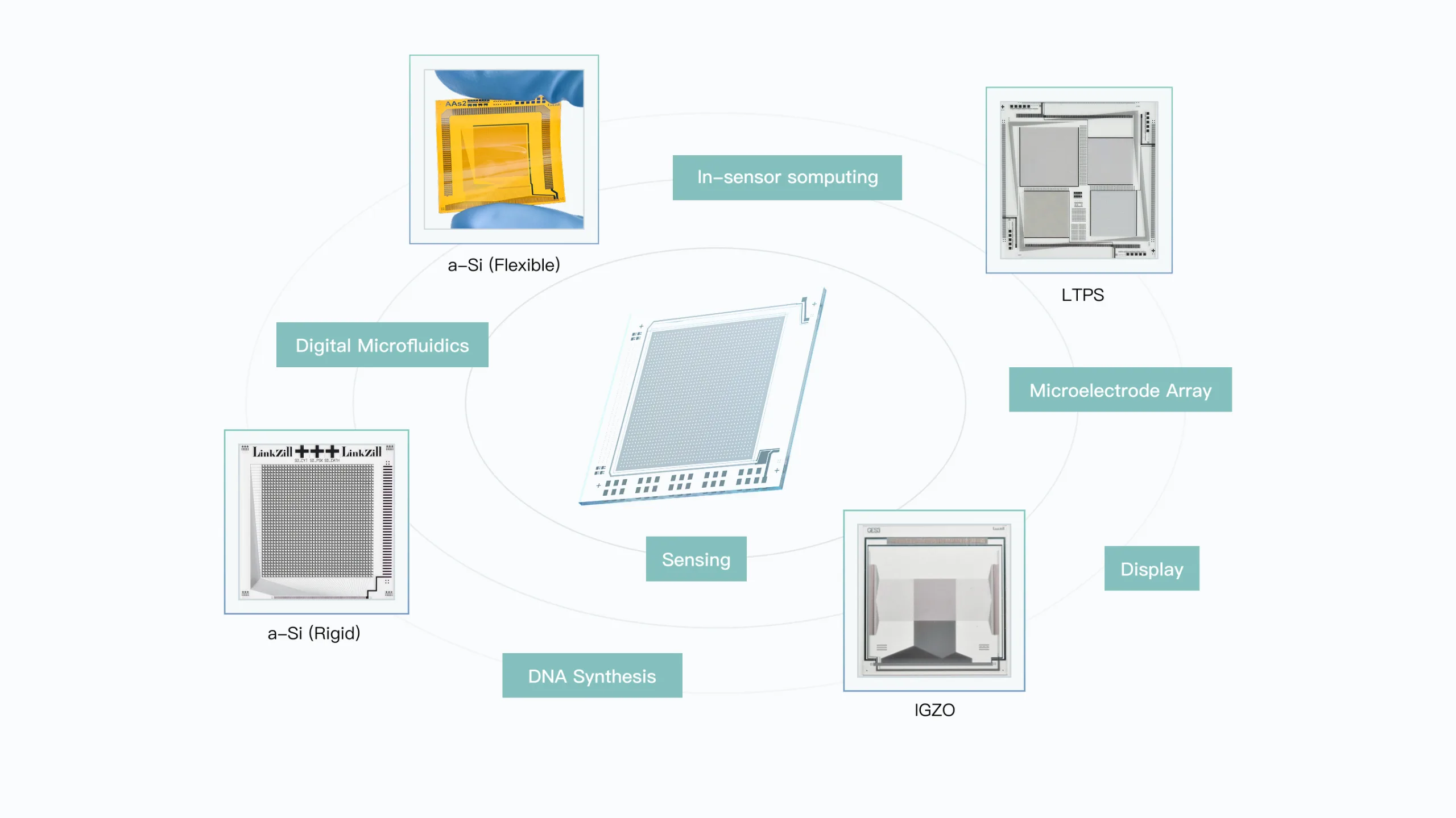

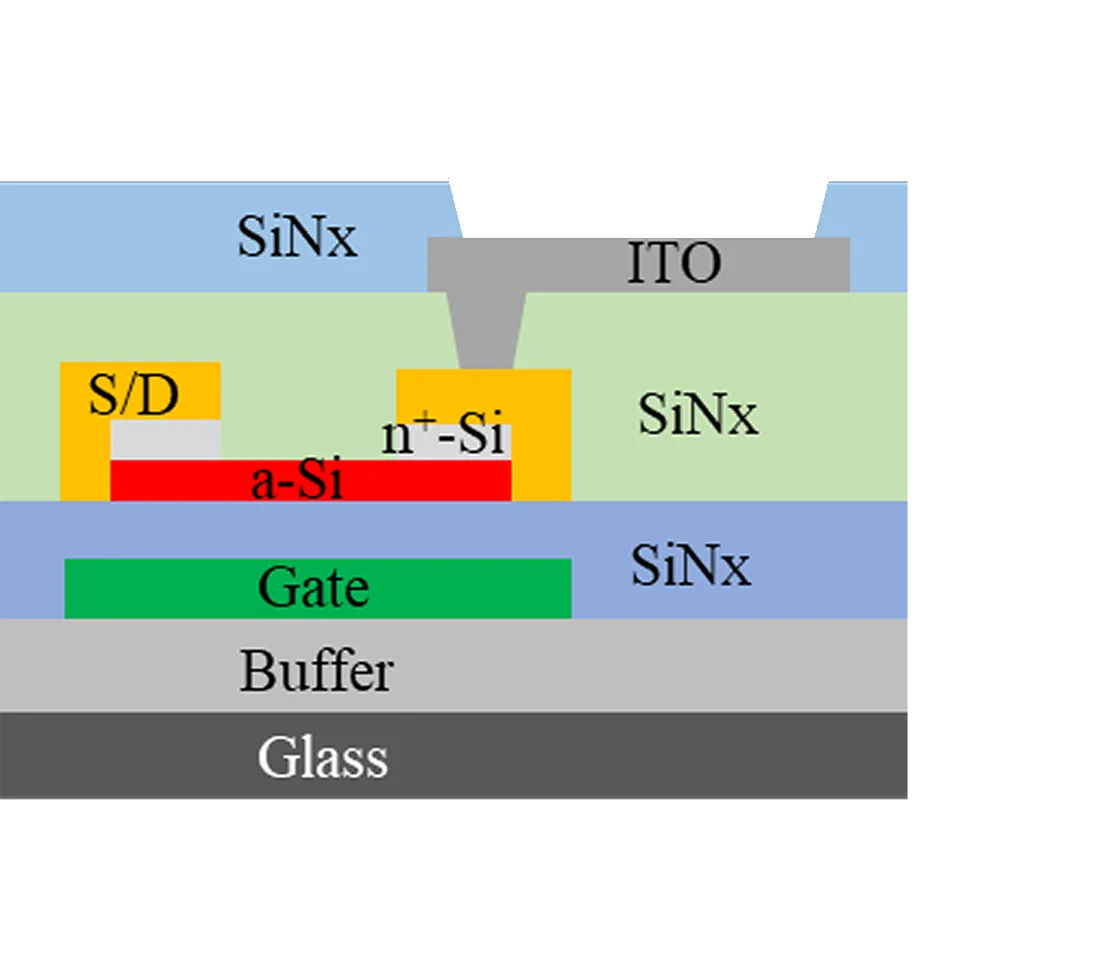

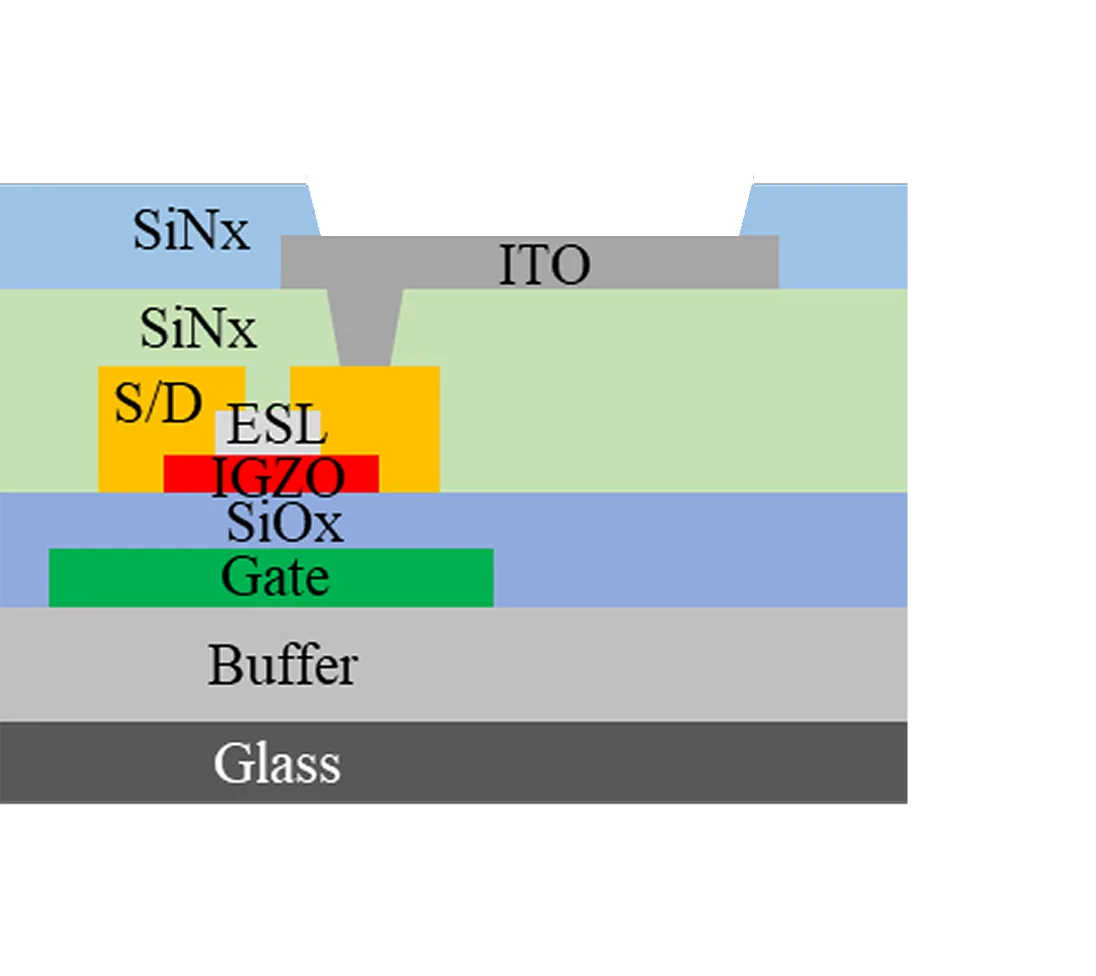

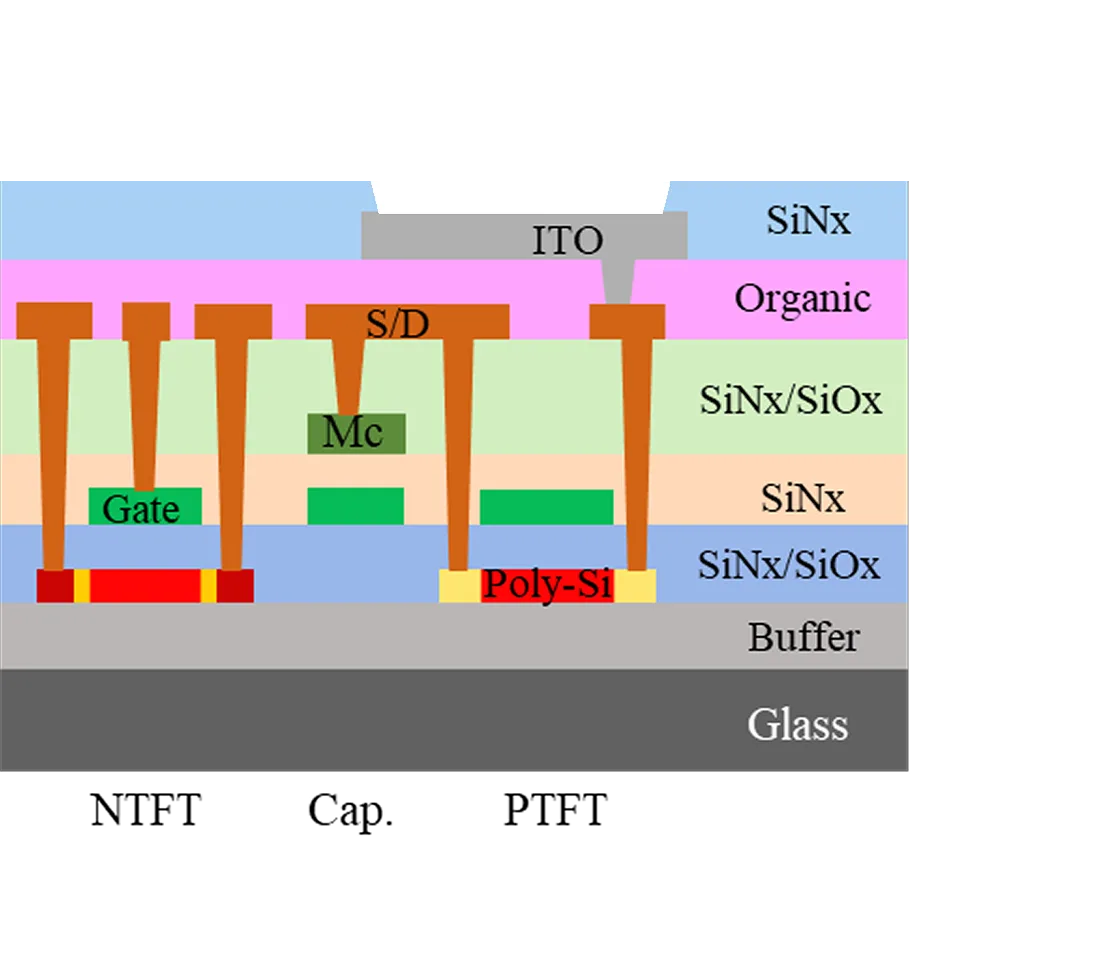

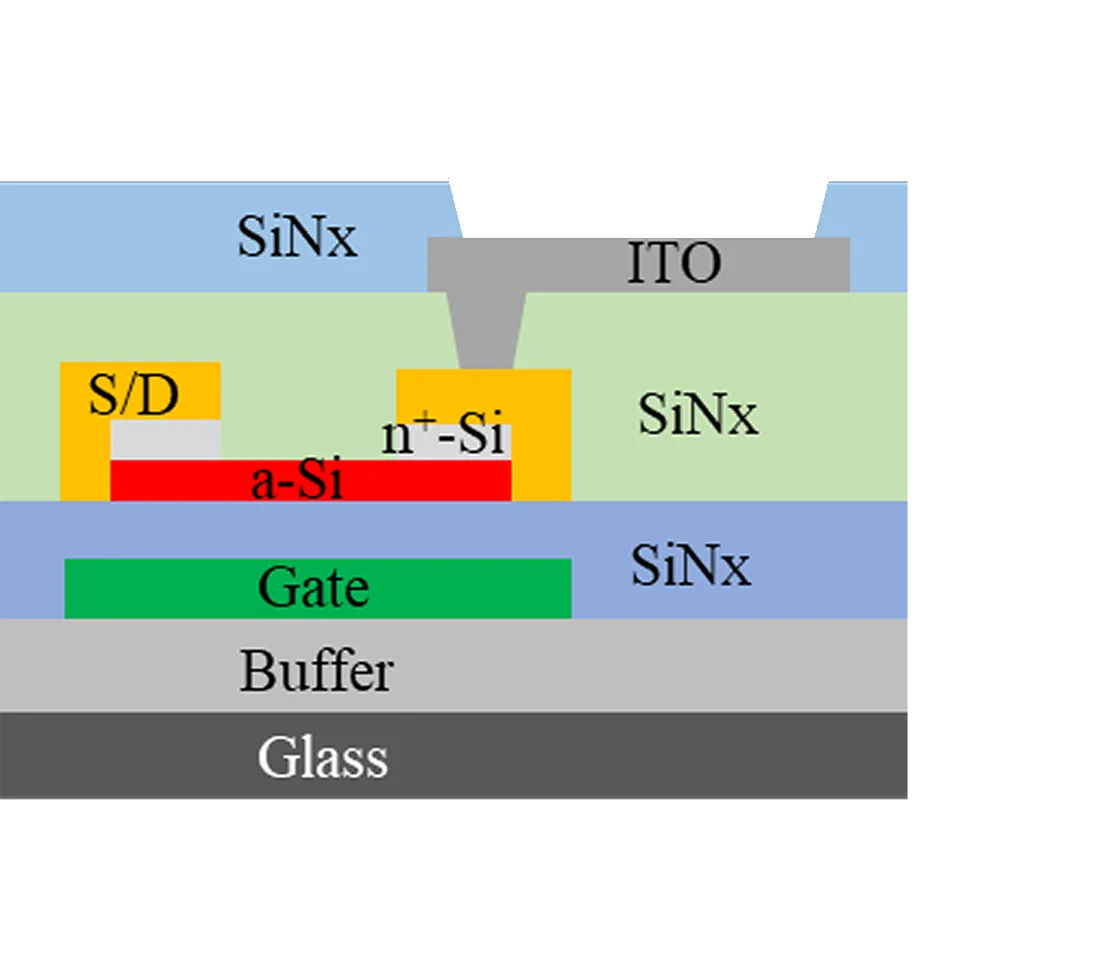

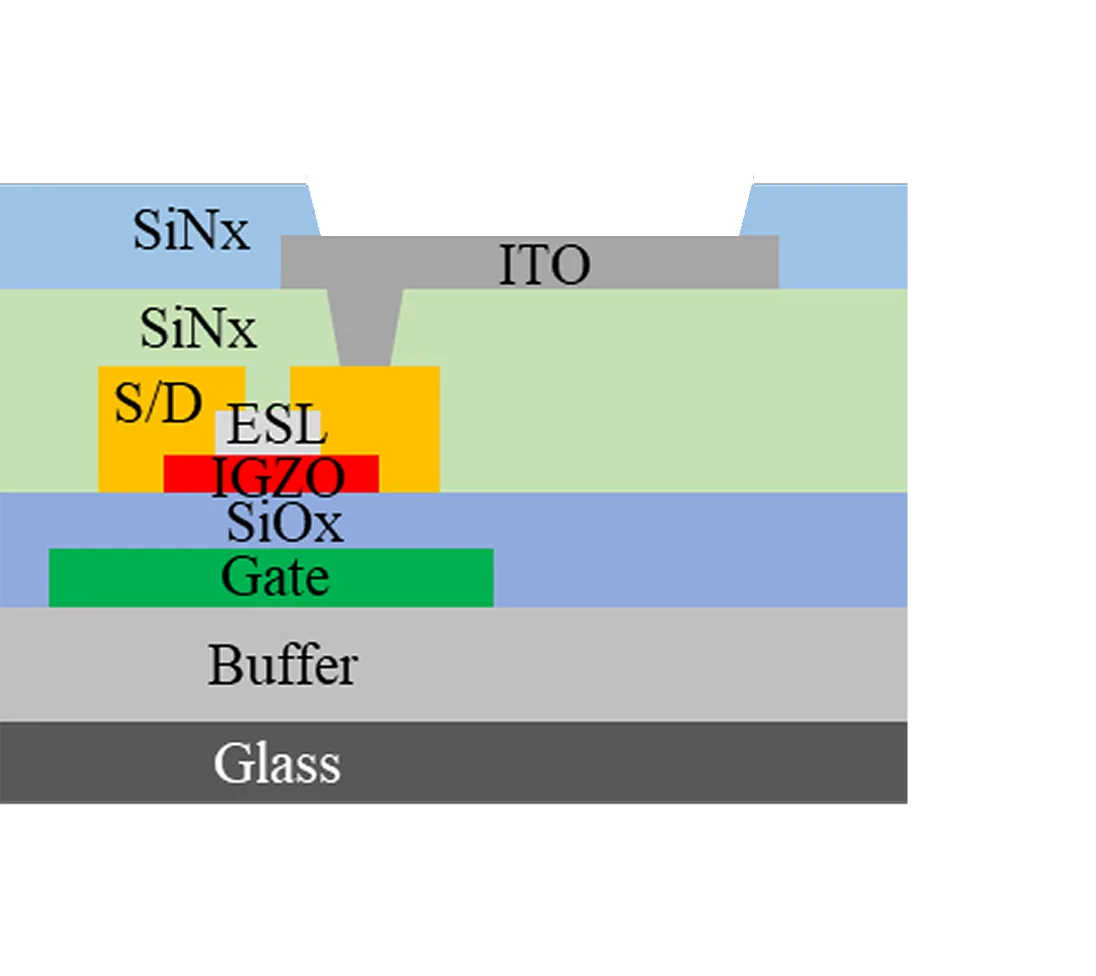

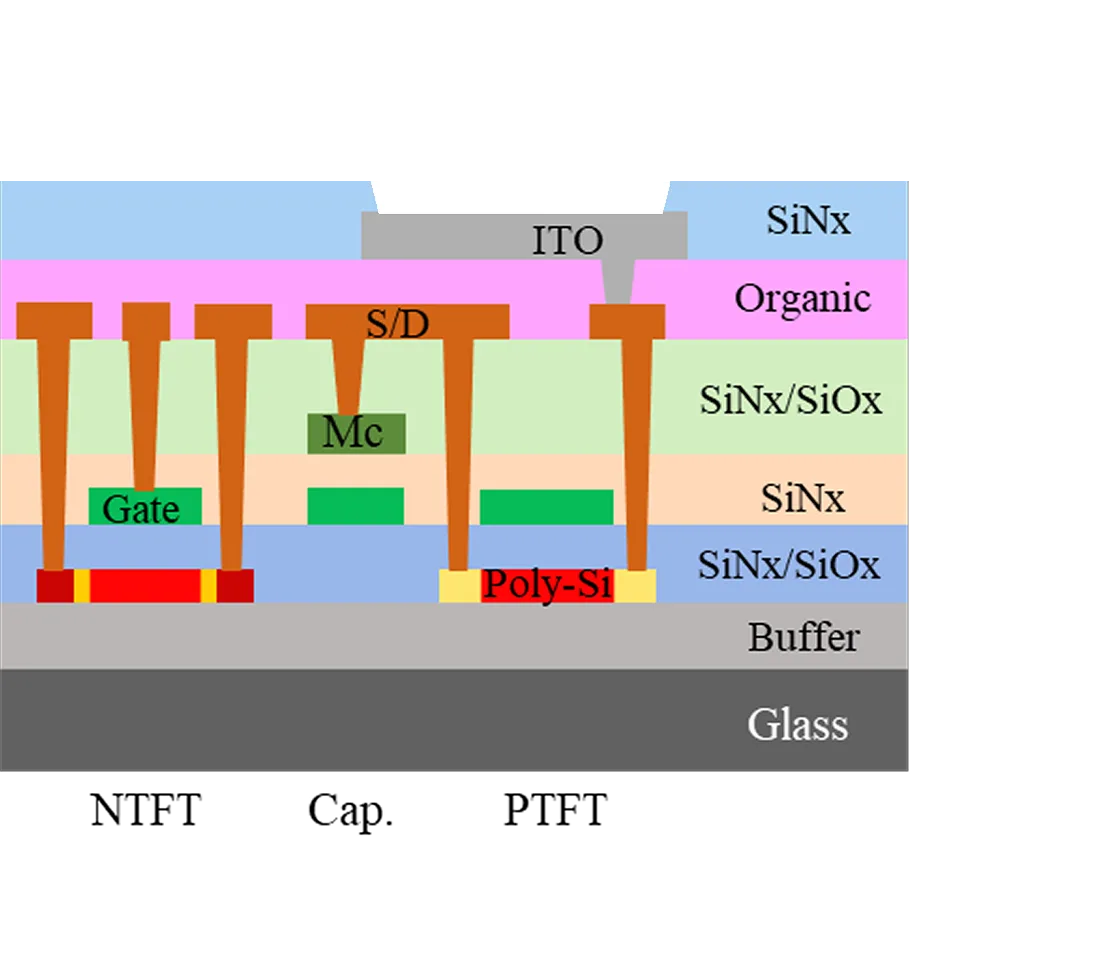

LinkZill offers TFT customized services covering three major TFT technology platforms—amorphous silicon (a-Si), oxide (IGZO), and low-temperature poly-silicon (LTPS), which can support large-scale displays, high-end displays and high-performance sensors, and medium-to-small high-resolution displays applications.

TFT chips are fabricated on either mass-production or pilot lines under rigorous quality regimes. Leveraging state-of-the-art equipment and automated workflows can ensure the consistently high yields, exceptional uniformity, and reliable device performance.

| a-Si (NTFT) | IGZO (NTFT) | LTPS (NTFT+PTFT) | |

| Process Technology / Process Flow | 6-Mask (Bottom-Gate BCE) | 8-Mask (Bottom-Gate ESL) | 11-Mask (Top-Gate Self-Aligned) |

| Layer Stack / Layer Structure |

|

|

|

| Foundry Generation / Manufacturing Node | Gen4.5 | Gen4.5 | Gen5.5 |

| Maximum Custom Area | 330mm × 440mm | 330mm × 440mm | 600mm × 700mm |

| Minimum Device Channel Length | 6μm | 10μm | 3μm |

| Minimum Line Width / Spacing | 4.5μm/4.5μm | 3μm/3μm | 3μm/3μm |

| Substrate Type | Rigid / Flexible | Rigid | |

| a-Si (NTFT) | IGZO (NTFT) | LTPS (NTFT+PTFT) | |

| Process Technology / Process Flow | 6-Mask (Bottom-Gate BCE) | 8-Mask (Bottom-Gate ESL) | 11-Mask (Top-Gate Self-Aligned) |

| Layer Stack / Layer Structure |

|

|

|

| Foundry Generation / Manufacturing Node | Gen4.5 | Gen4.5 | Gen5.5 |

| Maximum Custom Area | 330mm × 440mm | 330mm × 440mm | 600mm × 700mm |

| Minimum Device Channel Length | 6μm | 10μm | 3μm |

| Minimum Line Width / Spacing | 4.5μm/4.5μm | 3μm/3μm | 3μm/3μm |

| Substrate Type | Rigid / Flexible | Rigid | |

Hardware System Solutions

LinkZill maintains a dedicated electrical engineering (EE) development team specializing in hardware design, embedded/FPGA development, and host-computer interface design. Aligned with customer requirements, we architect optimal hardware systems and deliver comprehensive, turnkey hardware system solutions.

Our system customization capabilities include designing hardware for voltage and current readout and driving, as well as resistance and capacitance measurement. We also engineer drive and readout hardware systems tailored specifically for TFT arrays and interdigitated array configurations.

| Solutions |

Electrical Parameters |

Range |

Number of Channels/ Array Size |

Terminal | Applications |

|

Discrete Device Measurement System |

Resistance | 1Ω~10MΩ | 1–36 Channels | Phone/PC |

• OECT Measurement

• Flexible Electronics Measurement • Transistor Measurement • Sensor Measurement |

| Current | ±0.1nA~±1mA | ||||

| Voltage | ±10V | ||||

|

Array Driving System |

Voltage |

• Row-Select Voltage:±15V • Data Voltage:±10V • Common Electrode Voltage:±10V • Load Current<200mA |

≤512 × 512 | PC | Array Display |

|

Array Readout System |

Resistance | 10Ω~1MΩ | ≤64 × 64 | Phone/PC |

• Optical Array Sensing

• Pressure Array Sensing |

| Current | 0.1nA~150nA | ≤512 × 512 |

| Solutions | Electrical Parameters | Range | Number of Channels / Array Size | Terminal | Applications |

| Discrete Device Measurement System | Resistance | 1Ω ~ 10MΩ | 1–36 Channels | Phone / PC |

• OECT Measurement

• Flexible Electronics Measurement • Transistor Measurement • Sensor Measurement |

| Current | ±0.1nA ~ ±1mA | ||||

| Voltage | ±10V | ||||

| Array Driving System | Voltage |

• Row-Select Voltage:±15V

• Data Voltage:±10V • Common Electrode Voltage:±10V • Load Current<200mA |

≤512 × 512 | PC | Array Display |

| Array Readout System | Resistance | 10Ω~1MΩ | ≤64 × 64 | Phone / PC |

• Optical Array Sensing

• Pressure Array Sensing |

| Current | 0.1nA~150nA | ≤512 × 512 |